# LAMPIRAN 1 LISTING PROGRAM

| /****************                                      |

|--------------------------------------------------------|

| ****                                                   |

| This program was produced by the                       |

| CodeWizardAVR V2.05.0 Professional                     |

| Automatic Program Generator                            |

| © Copyright 1998-2010 Pavel Haiduc, HP InfoTech s.r.l. |

| http://www.hpinfotech.com                              |

|                                                        |

| Project:                                               |

| Version:                                               |

| Date : 7/10/2014                                       |

| Author: NeVaDa                                         |

| Company:                                               |

| Comments:                                              |

|                                                        |

| Chip type : ATmega16                                   |

| Program type : Application                             |

| AVR Core Clock frequency: 11.059200 MHz                |

: Small

Memory model

External RAM size : 0

```

Data Stack size : 128

*******************

***/

#include <mega16.h>

#include <stdlib.h>

#include <delay.h>

// Alphanumeric LCD Module functions

#include <alcd.h>

// Declare your global variables here

unsigned char buff[16];

float v;

void main(void)

// Declare your local variables here

// Input/Output Ports initialization

// Port A initialization

// Func7=In Func6=In Func5=In Func4=In Func3=In

Func2=In Func1=In Func0=In

```

```

// State7=T State6=T State5=T State4=T State3=T State2=T

State1=T State0=T

PORTA=0x00;

DDRA=0x00;

// Port B initialization

// Func7=In Func6=In Func5=In Func4=In Func3=In

Func2=In Func1=In Func0=In

// State7=T State6=T State5=T State4=T State3=T State2=T

State1=T State0=T

PORTB=0x00;

DDRB=0x00;

// Port C initialization

// Func7=In Func6=In Func5=In Func4=In Func3=In

Func2=In Func1=In Func0=In

// State7=T State6=T State5=T State4=T State3=T State2=T

State1=T State0=T

PORTC=0x00;

DDRC=0x00;

// Port D initialization

// Func7=In Func6=In Func5=In Func4=In Func3=In

Func2=In Func1=In Func0=In

```

```

// State7=T State6=T State5=T State4=T State3=T State2=T

State1=T State0=T

PORTD=0x00;

DDRD=0x00;

// Timer/Counter 0 initialization

// Clock source: System Clock

// Clock value: Timer 0 Stopped

// Mode: Normal top=0xFF

// OC0 output: Disconnected

TCCR0=0x00;

TCNT0=0x00;

OCR0=0x00;

// Timer/Counter 1 initialization

// Clock source: T1 pin Falling Edge

// Mode: Normal top=0xFFFF

// OC1A output: Discon.

// OC1B output: Discon.

// Noise Canceler: Off

// Input Capture on Falling Edge

// Timer1 Overflow Interrupt: Off

// Input Capture Interrupt: Off

// Compare A Match Interrupt: Off

```

```

// Compare B Match Interrupt: Off

TCCR1A=0x00;

TCCR1B=0x06;

TCNT1H=0x00;

TCNT1L=0x00;

ICR1H=0x00;

ICR1L=0x00;

OCR1AH=0x00;

OCR1AL=0x00;

OCR1BH=0x00;

OCR1BL=0x00;

// Timer/Counter 2 initialization

// Clock source: System Clock

// Clock value: Timer2 Stopped

// Mode: Normal top=0xFF

// OC2 output: Disconnected

ASSR=0x00;

TCCR2=0x00;

TCNT2=0x00;

OCR2 = 0x00;

// External Interrupt(s) initialization

// INT0: Off

```

```

// INT1: Off

// INT2: Off

MCUCR=0x00;

MCUCSR=0x00;

// Timer(s)/Counter(s) Interrupt(s) initialization

TIMSK=0x00;

// USART initialization

// USART disabled

UCSRB=0x00;

// Analog Comparator initialization

// Analog Comparator: Off

// Analog Comparator Input Capture by Timer/Counter 1: Off

ACSR=0x80:

SFIOR=0x00;

// ADC initialization

// ADC disabled

ADCSRA=0x00;

// SPI initialization

// SPI disabled

```

```

SPCR=0x00;

// TWI initialization

// TWI disabled

TWCR=0x00;

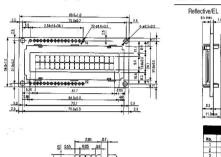

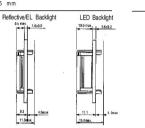

// Alphanumeric LCD initialization

// Connections specified in the

// ProjectlConfigurelC CompilerlLibrarieslAlphanumeric LCD

menu:

// RS - PORTC Bit 0

// RD - PORTC Bit 1

// EN - PORTC Bit 2

// D4 - PORTC Bit 4

// D5 - PORTC Bit 5

// D6 - PORTC Bit 6

// D7 - PORTC Bit 7

// Characters/line: 16

lcd_init(16);

lcd_clear();

lcd_gotoxy(0,0);

lcd_putsf("Anemometer");

lcd\_gotoxy(0,1);

lcd_putsf("By Megan");

```

```

delay_ms(5000);

while (1)

{

// Place your code here

TCNT1H=0x00;

TCNT1L=0x00;

TCCR1A=0x00;

TCCR1B=0x06;

delay_ms(1000);

TCCR1B=0;

v=((float)0.5652*TCNT1);

ftoa(v,2,buff);

lcd_clear();

lcd_gotoxy(0,0);

lcd_putsf("Anemometer");

lcd\_gotoxy(0,1);

lcd_putsf("v = ");

lcd_puts(buff);

lcd_putsf(" km/jam");

};

}

```

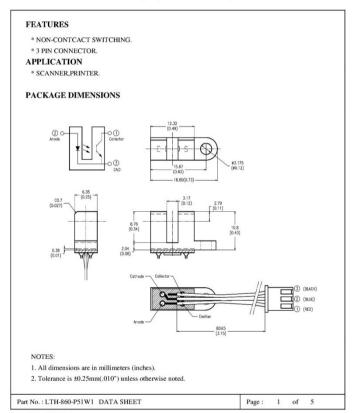

#### **Features**

- High-performance, Low-power Atmel® AVR® 8-bit Microcontroller

Advanced RISC Architecture

- - 131 Powerful Instructions Most Single-clock Cycle Execution

- 32 × 8 General Purpose Working Registers

- Substantial Purpose Working Reg

Fully Static Operation

Up to 16 MIPS Throughput at 16 MHz

On-chip 2-cycle Multiplier

- High Endurance Non-volatile Memory segments

- 16 Kbytes of In-System Self-programmable Flash program memory

- 512 Bytes EEPROM 1 Kbyte Internal SRAM

- Write/Erase Cycles: 10,000 Flash/100,000 EEPROM

- Data retention: 20 years at 85°C/100 years at 25°C

- Optional Boot Code Section with Independent Lock Bits

- In-System Programming by On-chip Boot Program True Read-While-Write Operation

- Programming Lock for Software Security

- JTAG (IEEE std. 1149.1 Compliant) Interface

- Boundary-scan Capabilities According to the JTAG Standard

Extensive On-chip Debug Support

- Programming of Flash, EEPROM, Fuses, and Lock Bits through the JTAG Interface

- Peripheral Features

- Two 8-bit Timer/Counters with Separate Prescalers and Compare Modes

- One 16-bit Timer/Counter with Separate Prescaler, Compare Mode, and Capture Mode

- Real Time Counter with Separate Oscillator

- Four PWM Channels

- 8-channel, 10-bit ADC

- 8 Single-ended Channels

7 Differential Channels in TQFP Package Only

- 2 Differential Channels with Programmable Gain at 1x, 10x, or 200x

- Byte-oriented Two-wire Serial Interface

Programmable Serial USART

- Master/Slave SPI Serial Interface

- Programmable Watchdog Timer with Separate On-chip Oscillator

- On-chip Analog Comparator

- Special Microcontroller Features

- Power-on Reset and Programmable Brown-out Detection

- Internal Calibrated RC Oscillator External and Internal Interrupt Sources

- Six Sleep Modes: Idle, ADC Noise Reduction, Power-save, Power-down, Standby

- and Extended Standby

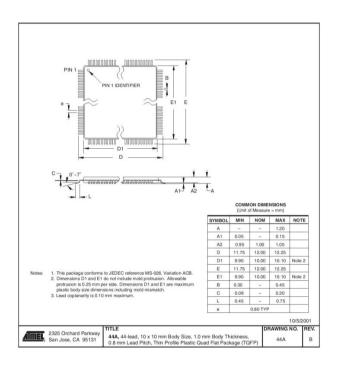

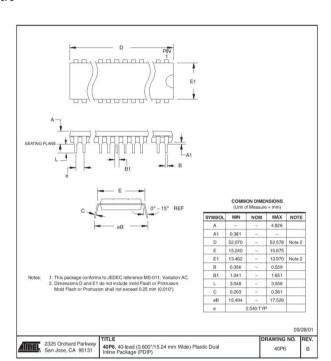

- I/O and Packages

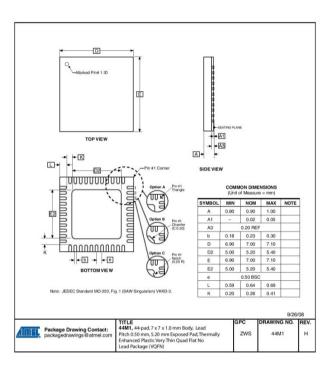

- 32 Programmable I/O Lines 40-pin PDIP, 44-lead TQFP, and 44-pad QFN/MLF

- 4.5V 5.5V for ATmega16

- · Speed Grades

- 0 8 MHz for ATmega16L

- 0 16 MHz for ATmega16

Power Consumption @ 1 MHz, 3V, and 25°C for ATmega16L - Active: 1.1 mA

- Idle Mode: 0.35 mA

- Power-down Mode: < 1 μA</li>

8-bit **AVR**® Microcontroller with 16K Bytes In-System **Programmable** Flash

ATmega16 ATmega16L

Summary

Rev. 2466TS-AVR-07/10

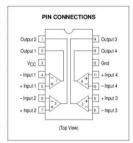

# Pin Configurations

Figure 1. Pinout ATmega16

# Disclaimer

Typical values contained in this datasheet are based on simulations and characterization of other AVR microcontrollers manufactured on the same process technology. Min and Max values will be available after the device is characterized.

# Overview

The ATmega16 is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISC architecture. By executing powerful instructions in a single clock cycle, the ATmega16 achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed.

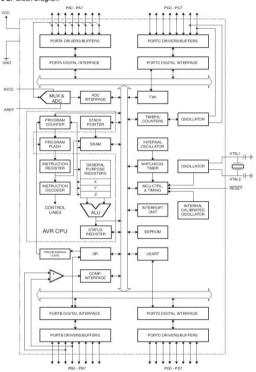

# **Block Diagram**

Figure 2. Block Diagram

The AVR core combines a rich instruction set with 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.

The ATmega16 provides the following features: 16 Kbytes of In-System Programmable Flash Program memory with Read-While-Write capabilities, 512 bytes EEPROM, 1 Kbyte SRAM, 32 general purpose I/O lines, 32 general purpose working registers, a JTAG interface for Boundaryscan, On-chip Debugging support and programming, three flexible Timer/Counters with compare modes. Internal and External Interrupts, a serial programmable USART, a byte oriented Two-wire Serial Interface, an 8-channel, 10-bit ADC with optional differential input stage with programmable gain (TQFP package only), a programmable Watchdog Timer with Internal Oscillator, an SPI serial port, and six software selectable power saving modes. The Idle mode stops the CPU while allowing the USART, Two-wire interface, A/D Converter, SRAM, Timer/Counters, SPI port, and interrupt system to continue functioning. The Power-down mode saves the register contents but freezes the Oscillator, disabling all other chip functions until the next External Interrupt or Hardware Reset. In Power-save mode, the Asynchronous Timer continues to run. allowing the user to maintain a timer base while the rest of the device is sleeping. The ADC Noise Reduction mode stops the CPU and all I/O modules except Asynchronous Timer and ADC, to minimize switching noise during ADC conversions. In Standby mode, the crystal/resonator Oscillator is running while the rest of the device is sleeping. This allows very fast start-up combined with low-power consumption. In Extended Standby mode, both the main Oscillator and the Asynchronous Timer continue to run.

The device is manufactured using Atmel's high density nonvolatile memory technology. The Onchip ISP Flash allows the program memory to be reprogrammed in-system through an SPI serial interface, by a conventional nonvolatile memory programmer, or by an On-chip Boot program running on the AVR core. The boot program can use any interface to download the application program in the Application Flash memory. Software in the Boot Flash section will continue to run while the Application Flash section is updated, providing true Read-While-Write operation. By combining an 8-bit RISC CPU with In-System Self-Programmable Flash on a monolithic chip, the Atmel ATmega16 is a powerful microcontroller that provides a highly-flexible and cost-effective solution to many embedded control applications.

The ATmega16 AVR is supported with a full suite of program and system development tools including: C compilers, macro assemblers, program debugger/simulators, in-circuit emulators, and evaluation kits.

# Pin Descriptions

VCC Digital supply voltage.

GND Ground.

Port A (PA7..PA0) Port A serves as the analog inputs to the A/D Converter.

Port A also serves as an 8-bit bi-directional I/O port, if the A/D Converter is not used. Port pins can provide internal pull-up resistors (selected for each bit). The Port A output buffers have symmetrical drive characteristics with both high sink and source capability. When pins PA0 to PA7 are used as inputs and are externally pulled low, they will source current if the internal pull-up resistors are activated. The Port A pins are tri-stated when a reset condition becomes active, even if the clock is not running.

# Port B (PB7..PB0)

Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated. The Port B pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port B also serves the functions of various special features of the ATmega16 as listed on page

# Port C (PC7..PC0)

Port C is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port C output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port C pins that are externally pulled low will source current if the pull-up resistors are activated. The Port C pins are tri-stated when a reset condition becomes active, even if the clock is not running. If the JTAG interface is enabled, the pull-up resistors on pins PC5(TDI), PC3(TMS) and PC2(TCK) will be activated even if a reset occurs.

Port C also serves the functions of the JTAG interface and other special features of the ATmega16 as listed on page 61.

# Port D (PD7..PD0)

Port D is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port D output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port D pins that are externally pulled low will source current if the pull-up resistors are activated. The Port D pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port D also serves the functions of various special features of the ATmega16 as listed on page

Reset Input. A low level on this pin for longer than the minimum pulse length will generate a reset, even if the clock is not running. The minimum pulse length is given in Table 15 on page 38. Shorter pulses are not guaranteed to generate a reset.

XTAL1 Input to the inverting Oscillator amplifier and input to the internal clock operating circuit.

XTAL2 Output from the inverting Oscillator amplifier.

AVCC AVCC is the supply voltage pin for Port A and the A/D Converter. It should be externally con-

nected to V<sub>CC</sub>, even if the ADC is not used. If the ADC is used, it should be connected to V<sub>CC</sub>

through a low-pass filter.

AREF AREF is the analog reference pin for the A/D Converter.

# RESET

Resources

A comprehensive set of development tools, application notes and datasheets are available for download on http://www.atmel.com/avr.

**Data Retention**

Reliability Qualification results show that the projected data retention failure rate is much less than 1 PPM over 20 years at  $85\,^{\circ}\!\text{C}$  or 100 years at  $25\,^{\circ}\!\text{C}$ .

# **Register Summary**

| Address                    | Name          | Bit 7            | Bit 6                               | Bit 5             | Bit 4   | Bit 3           | Bit 2          | Bit 1   | Bit 0  | Page              |

|----------------------------|---------------|------------------|-------------------------------------|-------------------|---------|-----------------|----------------|---------|--------|-------------------|

| \$3F (\$5F)                | SREG          | 1                | T                                   | н                 | s       | V               | N              | Z       | С      | 9                 |

| \$3E (\$5E)                | SPH           | -                | -                                   | -                 | -       | -               | SP10           | SP9     | SP8    | 12                |

| \$3D (\$5D)                | SPL           | SP7              | SP6                                 | SP5               | SP4     | SP3             | SP2            | SP1     | SP0    | 12                |

| \$3C (\$5C)                | OCR0          | Timer/Counter    | 0 Output Compar                     | e Register        |         |                 |                |         |        | 85                |

| \$3B (\$5B)                | GICR          | INT1             | INT0                                | INT2              | -       | -               | -              | IVSEL   | IVCE   | 48, 69            |

| \$3A (\$5A)                | GIFR          | INTF1            | INTF0                               | INTF2             | -       | -               | -              | -       | -      | 70                |

| \$39 (\$59)                | TIMSK         | OCIE2            | TOIE2                               | TICIE1            | OCIE1A  | OCIE1B          | TOIE1          | OCIE0   | TOIE0  | 85, 115, 133      |

| \$38 (\$58)                | TIFR          | OCF2             | TOV2                                | ICF1              | OCF1A   | OCF1B           | TOV1           | OCF0    | TOV0   | 86, 115, 133      |

| \$37 (\$57)                | SPMCR         | SPMIE            | RWWSB                               | -                 | RWWSRE  | BLBSET          | PGWRT          | PGERS   | SPMEN  | 250               |

| \$36 (\$56)                | TWCR          | TMNT             | TWEA                                | TWSTA             | TWSTO   | TWWC            | TWEN           | -       | TWIE   | 180               |

| \$35 (\$55)                | MCUCR         | SM2              | SE                                  | SM1               | SM0     | ISC11           | ISC10          | ISC01   | ISC00  | 32, 68            |

| \$34 (\$54)                | MCUCSR        | JTD              | ISC2                                | -                 | JTRF    | WDRF            | BORF           | EXTRF   | PORF   | 41, 69, 231       |

| \$33 (\$53)                | TCCRO         | FOC0             | WGM00                               | COM01             | COM00   | WGM01           | CS02           | CS01    | CS00   | 83                |

| \$32 (\$52)                | TCNT0         | Timer/Counter    | 0 (8 Bits)                          |                   |         |                 |                |         |        | 85                |

| marill (marrill)           | OSCCAL        | Oscillator Calif | bration Register                    |                   |         |                 |                |         |        | 30                |

| \$31(1) (\$51)(1)          | OCDR          | On-Chip Debu     | g Register                          |                   |         |                 |                |         |        | 227               |

| \$30 (\$50)                | SFIOR         | ADTS2            | ADTS1                               | ADTS0             | -       | ACME            | PUD            | PSR2    | PSR10  | 57,88,134,201,221 |

| \$2F (\$4F)                | TCCR1A        | COM1A1           | COM1A0                              | COM1B1            | COM1B0  | FOC1A           | FOC1B          | WGM11   | WGM10  | 110               |

| \$2E (\$4E)                | TCCR1B        | ICNC1            | ICES1                               | -                 | WGM13   | WGM12           | CS12           | CS11    | CS10   | 113               |

| \$2D (\$4D)                | TCNT1H        |                  | 1 - Counter Regi                    | ster High Byte    |         |                 |                |         |        | 114               |

| \$2C (\$4C)                | TCNT1L        |                  | 1 - Counter Regi                    |                   |         |                 |                |         |        | 114               |

| \$2B (\$4B)                | OCR1AH        |                  |                                     | are Register A Hi | gh Byte |                 |                |         |        | 114               |

| \$2A (\$4A)                | OCR1AL        |                  |                                     | are Register A Lo |         |                 |                |         |        | 114               |

| \$29 (\$49)                | OCR18H        |                  |                                     | are Register B Hi |         |                 |                |         |        | 114               |

| \$28 (\$48)                | OCR1BL        |                  |                                     | are Register B Lo |         |                 |                |         |        | 114               |

| \$27 (\$47)                | ICR1H         |                  |                                     | Register High By  |         |                 |                |         |        | 114               |

| \$26 (\$46)                | ICR1L         |                  |                                     | Register Low By   |         |                 |                |         |        | 114               |

| \$25 (\$45)                | TCCR2         | FOC2             | WGM20                               | COM21             | COM20   | WGM21           | CS22           | CS21    | CS20   | 128               |

| \$24 (\$44)                | TCNT2         | Timer/Counter    |                                     | COM21             | COM20   | VVGWIZI         | 0322           | 0021    | 0020   | 130               |

| \$23 (\$43)                | OCR2          |                  | 2 Output Compar                     | a Panister        |         |                 |                |         |        | 130               |

| \$22 (\$42)                | ASSR          | Timenounte       | L output outspan                    | C regioner        | 7500    | AS2             | TCN2UB         | OCR2UB  | TCR2UB | 131               |

| \$21 (\$41)                | WDTCR         | -                | -                                   | _                 | WDTOE   | WDE             | WDP2           | WDP1    | WDP0   | 43                |

| 321 (341)                  | UBRRH         | URSEL            | -                                   | -                 | WOTOE   | WDE             |                | R[11:8] | VVDPO  |                   |

| \$20 (\$40)                | UCSRC         | URSEL            | UMSEL                               | UPM1              | UPM0    | USBS            | UCSZ1          | UCSZ0   | UCPOL  | 167<br>166        |

| \$1F (\$3F)                | EEARH         | UNSEL            | UMSEL                               | OPMI              | OPINO - | 0363            | 00321          | 00320   | EEAR8  | 19                |

|                            |               | FEDDOM A 44      | - Desisted to                       | P. 4-             | -       | -               | -              | _       | EEARO  |                   |

| \$1E (\$3E)                | EEARL         |                  | ress Register Lov                   | w Byte            |         |                 |                |         |        | 19                |

| \$1D (\$3D)                | EEDR          | EEPROM Date      | a Register                          |                   | _       | FEDIE           | Four           | FFIRE   | FERE   | 19                |

| \$1C (\$3C)                | EECR<br>PORTA | PORTA7           | PORTA6                              | PORTA5            | PORTA4  | EERIE<br>PORTA3 | EEMWE          | PORTA1  | PORTAG | 19                |

| \$1B (\$3B)                | DDRA          | DDA7             | DDA6                                | DDA5              | DDA4    | DDA3            | PORTA2<br>DDA2 | DDA1    | DDAG   | 66                |

| \$1A (\$3A)                |               |                  |                                     |                   |         |                 |                |         |        |                   |

| \$19 (\$39)                | PINA          | PINA7            | PINA6                               | PINA5             | PINA4   | PINA3           | PINA2          | PINA1   | PINAO  | 66                |

| \$18 (\$38)                | PORTB         | PORTB7           | PORTB6                              | PORTB5            | PORTB4  | PORTB3          | PORTB2         | PORTB1  | PORTB0 | 66                |

| \$17 (\$37)                | DDRB          | DDB7             | DDB6                                | DDB5              | DDB4    | DDB3            | DDB2           | DDB1    | DDB0   | 66                |

| \$16 (\$36)                | PINB          | PINB7            | PINB6                               | PINB5             | PINB4   | PINB3           | PINB2          | PINB1   | PINBO  | 66                |

| \$15 (\$35)                | PORTC         | PORTC7           | PORTC6                              | PORTC5            | PORTC4  | PORTC3          | PORTC2         | PORTC1  | PORTC0 | 67                |

| \$14 (\$34)                | DDRC          | DDC7             | DDC6                                | DDC5              | DDC4    | DDC3            | DDC2           | DDC1    | DDC0   | 67                |

| \$13 (\$33)                | PINC          | PINC7            | PINC6                               | PINC5             | PINC4   | PINC3           | PINC2          | PINC1   | PINCO  | 67                |

| \$12 (\$32)                | PORTD         | PORTD7           | PORTD6                              | PORTD5            | PORTD4  | PORTD3          | PORTD2         | PORTD1  | PORTD0 | 67                |

| \$11 (\$31)                | DDRD          | DDD7             | DDD6                                | DDD5              | DDD4    | DDD3            | DDD2           | DDD1    | DDD0   | 67                |

| \$10 (\$30)                | PIND          | PIND7            | PIND6                               | PIND5             | PIND4   | PIND3           | PIND2          | PIND1   | PIND0  | 67                |

| \$0F (\$2F)                | SPDR          | SPI Data Reg     |                                     |                   |         |                 |                |         |        | 142               |

| \$0E (\$2E)                | SPSR          | SPIF             | WCOL                                | -                 | -       | -               | -              | -       | SPI2X  | 142               |

| \$0D (\$2D)                | SPCR          | SPIE             | SPE                                 | DORD              | MSTR    | CPOL            | CPHA           | SPR1    | SPR0   | 140               |

| \$0C (\$2C)                | UDR           | USART I/O D      |                                     |                   |         |                 |                |         |        | 163               |

| \$0B (\$2B)                | UCSRA         | RXC              | TXC                                 | UDRE              | FE      | DOR             | PE             | U2X     | MPCM   | 164               |

| \$0A (\$2A)                | UCSRB         | RXCIE            | TXCIE                               | UDRIE             | RXEN    | TXEN            | UCSZ2          | RXB8    | TXB8   | 165               |

| \$09 (\$29)                | UBRRL         | USART Baud       | Rate Register Lo                    | w Byte            |         |                 |                |         |        | 167               |

| \$08 (\$28)                | ACSR          | ACD              | ACBG                                | ACO               | ACI     | ACIE            | ACIC           | ACIS1   | ACIS0  | 202               |

|                            | ADMUX         | REFS1            | REFS0                               | ADLAR             | MUX4    | MUX3            | MUX2           | MUX1    | MUX0   | 217               |

| \$07 (\$27)                | ADCSRA        | ADEN             | ADSC                                | ADATE             | ADIF    | ADIE            | ADPS2          | ADPS1   | ADPS0  | 219               |

| \$07 (\$27)<br>\$06 (\$26) |               |                  |                                     |                   |         |                 |                |         |        |                   |

| \$06 (\$26)                |               | ADC Data Rec     | ister High Byte                     |                   |         |                 |                |         |        | 220               |

|                            | ADCH<br>ADCL  | ADC Data Reg     | gister High Byte<br>gister Low Byte |                   |         |                 |                |         |        | 220               |

| \$06 (\$26)<br>\$05 (\$25) | ADCH          | ADC Data Reg     |                                     | Register          |         |                 |                |         |        |                   |

| Address     | Name | Bit 7          | Bit 6                                     | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Page |

|-------------|------|----------------|-------------------------------------------|-------|-------|-------|-------|-------|-------|------|

| \$01 (\$21) | TWSR | TWS7           | TWS6                                      | TWS5  | TWS4  | TWS3  | -     | TWPS1 | TWPS0 | 181  |

| \$00 (\$20) | TWBR | Two-wire Seria | o-wire Serial Interface Bit Rate Register |       |       | 180   |       |       |       |      |

- Notes: 1. When the OCDEN Fuse is unprogrammed, the OSCCAL Register is always accessed on this address. Refer to the debugger specific documentation for details on how to use the OCDR Register.

2. Refer to the USART description for details on how to access UBRRH and UCSRC.

3. For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addresses should never be written.

- should never be written.

4. Some of the Status Flags are cleared by writing a logical one to them. Note that the CBI and SBI instructions will operate on all bits in the I/O Register, writing a one back into any flag read as set, thus clearing the flag. The CBI and SBI instructions work with registers \$00 to \$1F only.

# Instruction Set Summary

| Mnemonics                                                   | Operands                   | Description                                                                                                                                                                                                                                                                                                                                          | Operation                                                                                                                                                                                                                                                                                                                                                                                                        | Flags                                   | #Clocks                                                            |

|-------------------------------------------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--------------------------------------------------------------------|

| ARITHMETIC AND                                              | LOGIC INSTRUCTION          | s                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                  |                                         |                                                                    |

| ADD                                                         | Rd, Rr                     | Add two Registers                                                                                                                                                                                                                                                                                                                                    | Rd ← Rd + Rr                                                                                                                                                                                                                                                                                                                                                                                                     | Z,C,N,V,H                               | 1                                                                  |

| ADC                                                         | Rd, Rr                     | Add with Carry two Registers                                                                                                                                                                                                                                                                                                                         | $Rd \leftarrow Rd + Rr + C$                                                                                                                                                                                                                                                                                                                                                                                      | Z,C,N,V,H                               | 1                                                                  |

| ADIW                                                        | RdI,K                      | Add Immediate to Word                                                                                                                                                                                                                                                                                                                                | Rdh:Rdl ← Rdh:Rdl + K                                                                                                                                                                                                                                                                                                                                                                                            | Z,C,N,V,S                               | 2                                                                  |

| SUB                                                         | Rd, Rr                     | Subtract two Registers                                                                                                                                                                                                                                                                                                                               | Rd ← Rd - Rr                                                                                                                                                                                                                                                                                                                                                                                                     | Z,C,N,V,H                               | 1                                                                  |

| SUBI                                                        | Rd, K                      | Subtract Constant from Register                                                                                                                                                                                                                                                                                                                      | Rd ← Rd - K                                                                                                                                                                                                                                                                                                                                                                                                      | Z,C,N,V,H                               | 1                                                                  |

| SBC                                                         | Rd, Rr                     | Subtract with Carry two Registers                                                                                                                                                                                                                                                                                                                    | Rd ← Rd - Rr - C                                                                                                                                                                                                                                                                                                                                                                                                 | Z,C,N,V,H                               | 1                                                                  |

| SBCI                                                        | Rd, K                      | Subtract with Carry Constant from Reg.                                                                                                                                                                                                                                                                                                               | Rd ← Rd - K - C                                                                                                                                                                                                                                                                                                                                                                                                  | Z,C,N,V,H                               | 1                                                                  |

| SBIW                                                        | Rdl,K                      | Subtract Immediate from Word                                                                                                                                                                                                                                                                                                                         | Rdh:Rdl ← Rdh:Rdl - K                                                                                                                                                                                                                                                                                                                                                                                            | Z,C,N,V,S                               | 2                                                                  |

| AND                                                         | Rd, Rr                     | Logical AND Registers                                                                                                                                                                                                                                                                                                                                | Rd ← Rd • Rr                                                                                                                                                                                                                                                                                                                                                                                                     | Z,N,V                                   | 1                                                                  |

| ANDI                                                        | Rd, K                      | Logical AND Register and Constant                                                                                                                                                                                                                                                                                                                    | Rd ← Rd • K<br>Rd ← Rd ∨ Rr                                                                                                                                                                                                                                                                                                                                                                                      | Z,N,V<br>Z,N,V                          | 1                                                                  |

| ORI                                                         | Rd, Rr<br>Rd, K            | Logical OR Registers                                                                                                                                                                                                                                                                                                                                 | Rd ← Rd ∨ K                                                                                                                                                                                                                                                                                                                                                                                                      | Z,N,V                                   | 1 1                                                                |

| EOR                                                         | Rd, Rr                     | Logical OR Register and Constant<br>Exclusive OR Registers                                                                                                                                                                                                                                                                                           | Rd ← Rd ⊕ Rr                                                                                                                                                                                                                                                                                                                                                                                                     | ZN,V                                    | 1                                                                  |

| COM                                                         | Rd, Rr                     |                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                  |                                         | 1                                                                  |

| 0.0111                                                      | -110                       | One's Complement                                                                                                                                                                                                                                                                                                                                     | Rd ← SFF – Rd                                                                                                                                                                                                                                                                                                                                                                                                    | Z,C,N,V                                 |                                                                    |

| NEG<br>SBR                                                  | Rd<br>Rd.K                 | Two's Complement                                                                                                                                                                                                                                                                                                                                     | Rd ← \$00 − Rd<br>Rd ← Rd ∨ K                                                                                                                                                                                                                                                                                                                                                                                    | Z,C,N,V,H<br>Z,N,V                      | 1                                                                  |

|                                                             | Rd,K                       | Set Bit(s) in Register                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                  | Z,N,V                                   | 1                                                                  |

| CBR                                                         | Rd,K                       | Clear Bit(s) in Register<br>Increment                                                                                                                                                                                                                                                                                                                | Rd ← Rd + (3FF - K)<br>Rd ← Rd + 1                                                                                                                                                                                                                                                                                                                                                                               | ZN,V                                    | 1                                                                  |

|                                                             |                            |                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                  |                                         |                                                                    |

| DEC                                                         | Rd                         | Decrement                                                                                                                                                                                                                                                                                                                                            | Rd ← Rd − 1                                                                                                                                                                                                                                                                                                                                                                                                      | Z,N,V                                   | 1                                                                  |

| TST                                                         | Rd<br>Rd                   | Test for Zero or Minus<br>Clear Register                                                                                                                                                                                                                                                                                                             | $Rd \leftarrow Rd \bullet Rd$<br>$Rd \leftarrow Rd \oplus Rd$                                                                                                                                                                                                                                                                                                                                                    | Z,N,V<br>Z,N,V                          | 1                                                                  |

| SER                                                         | Rd                         |                                                                                                                                                                                                                                                                                                                                                      | Rd ← SFF                                                                                                                                                                                                                                                                                                                                                                                                         | None                                    | 1                                                                  |

| MUL                                                         | Rd. Rr                     | Set Register                                                                                                                                                                                                                                                                                                                                         | R1:R0 ← Rd x Rr                                                                                                                                                                                                                                                                                                                                                                                                  | Z.C                                     | 2                                                                  |

| MULS                                                        | Rd, Rr                     | Multiply Unsigned                                                                                                                                                                                                                                                                                                                                    | R1:R0 ← Rd x Rr                                                                                                                                                                                                                                                                                                                                                                                                  | Z,C                                     | 2                                                                  |

| MULSU                                                       | Rd, Rr                     | Multiply Signed                                                                                                                                                                                                                                                                                                                                      | R1:R0 ← Rd x Rr                                                                                                                                                                                                                                                                                                                                                                                                  | Z,C                                     | 2                                                                  |

| FMUL                                                        | Rd, Rr                     | Multiply Signed with Unsigned<br>Fractional Multiply Unsigned                                                                                                                                                                                                                                                                                        | R1:R0 ← (Rd x Rr) << 1                                                                                                                                                                                                                                                                                                                                                                                           | Z,C                                     | 2                                                                  |

| FMULS                                                       | Rd, Rr                     | Fractional Multiply Onsigned Fractional Multiply Signed                                                                                                                                                                                                                                                                                              | R1:R0 ← (Rd x Rr) << 1                                                                                                                                                                                                                                                                                                                                                                                           | Z,C                                     | 2                                                                  |

| FMULSU                                                      | Rd Rr                      | Fractional Multiply Signed with Unsigned                                                                                                                                                                                                                                                                                                             | R1:R0 ← (Rd x Rr) << 1                                                                                                                                                                                                                                                                                                                                                                                           | Z.C                                     | 2                                                                  |

| BRANCH INSTRUC                                              |                            | Fractional Mulippy Signed with Orisigned                                                                                                                                                                                                                                                                                                             | RING (ROXRI) 33 I                                                                                                                                                                                                                                                                                                                                                                                                | 2,0                                     | - 2                                                                |

| RJMP                                                        | k                          | Relative Jump                                                                                                                                                                                                                                                                                                                                        | PC ← PC + k + 1                                                                                                                                                                                                                                                                                                                                                                                                  | None                                    | 2                                                                  |

| IJMP                                                        | -                          | Indirect Jump to (Z)                                                                                                                                                                                                                                                                                                                                 | PC ←Z                                                                                                                                                                                                                                                                                                                                                                                                            | None                                    | 2                                                                  |

| JMP                                                         | k                          | Direct Jump                                                                                                                                                                                                                                                                                                                                          | PC ← k                                                                                                                                                                                                                                                                                                                                                                                                           | None                                    | 3                                                                  |

| RCALL                                                       | k                          | Relative Subroutine Call                                                                                                                                                                                                                                                                                                                             | PC ← PC + k + 1                                                                                                                                                                                                                                                                                                                                                                                                  | None                                    | 3                                                                  |

| ICALL                                                       |                            | Indirect Call to (Z)                                                                                                                                                                                                                                                                                                                                 | PC ← Z                                                                                                                                                                                                                                                                                                                                                                                                           | None                                    | 3                                                                  |

| CALL                                                        | k                          | Direct Subroutine Call                                                                                                                                                                                                                                                                                                                               | PC ←k                                                                                                                                                                                                                                                                                                                                                                                                            | None                                    | 4                                                                  |

| RET                                                         |                            | Subroutine Return                                                                                                                                                                                                                                                                                                                                    | PC ← STACK                                                                                                                                                                                                                                                                                                                                                                                                       | None                                    | 4                                                                  |

| RETI                                                        |                            | Interrupt Return                                                                                                                                                                                                                                                                                                                                     | PC ← STACK                                                                                                                                                                                                                                                                                                                                                                                                       | 1                                       | 4                                                                  |

| CPSE                                                        | Rd,Rr                      | Compare, Skip if Equal                                                                                                                                                                                                                                                                                                                               | if (Rd = Rr) PC ← PC + 2 or 3                                                                                                                                                                                                                                                                                                                                                                                    | None                                    | 1/2/3                                                              |

| CP                                                          | Rd,Rr                      | Compare                                                                                                                                                                                                                                                                                                                                              | Rd – Rr                                                                                                                                                                                                                                                                                                                                                                                                          | Z, N,V,C,H                              | - 1                                                                |

| CPC                                                         | Rd,Rr                      | Compare with Carry                                                                                                                                                                                                                                                                                                                                   | Rd - Rr - C                                                                                                                                                                                                                                                                                                                                                                                                      | Z, N,V,C,H                              | 1                                                                  |

| CPI                                                         | Rd,K                       | Compare Register with Immediate                                                                                                                                                                                                                                                                                                                      | Rd – K                                                                                                                                                                                                                                                                                                                                                                                                           | Z, N,V,C,H                              | 1                                                                  |

| SBRC                                                        | Rr, b                      | Skip if Bit in Register Cleared                                                                                                                                                                                                                                                                                                                      | if (Rr(b)=0) PC ← PC + 2 or 3                                                                                                                                                                                                                                                                                                                                                                                    | None                                    | 1/2/3                                                              |

| SBRS                                                        | Rr, b                      | Skip if Bit in Register is Set                                                                                                                                                                                                                                                                                                                       | if (Rr(b)=1) PC ← PC + 2 or 3                                                                                                                                                                                                                                                                                                                                                                                    | None                                    | 1/2/3                                                              |

| SBIC                                                        | P, b                       | Skip if Bit in I/O Register Cleared                                                                                                                                                                                                                                                                                                                  | if (P(b)=0) PC ← PC + 2 or 3                                                                                                                                                                                                                                                                                                                                                                                     | None                                    | 1/2/3                                                              |

| SBIS                                                        | P, b                       | Skip if Bit in I/O Register is Set                                                                                                                                                                                                                                                                                                                   | if (P(b)=1) PC ← PC + 2 or 3                                                                                                                                                                                                                                                                                                                                                                                     | None                                    | 1/2/3                                                              |

| BRBS                                                        | s, k                       | Branch if Status Flag Set                                                                                                                                                                                                                                                                                                                            | if (SREG(s) = 1) then PC←PC+k + 1                                                                                                                                                                                                                                                                                                                                                                                | None                                    | 1/2                                                                |

| BRBC                                                        | s, k                       | Branch if Status Flag Cleared                                                                                                                                                                                                                                                                                                                        | if (SREG(s) = 0) then PC←PC+k+1                                                                                                                                                                                                                                                                                                                                                                                  | None                                    | 1/2                                                                |

| BREQ                                                        | k                          | Branch if Equal                                                                                                                                                                                                                                                                                                                                      | if (Z = 1) then PC ← PC + k + 1                                                                                                                                                                                                                                                                                                                                                                                  | None                                    | 1/2                                                                |

| BRNE                                                        | k                          | Branch if Not Equal                                                                                                                                                                                                                                                                                                                                  | if (Z = 0) then PC ← PC + k + 1                                                                                                                                                                                                                                                                                                                                                                                  | None                                    | 1/2                                                                |